Schematic capture or schematic entry is a step in the design cycle of electronic design automation (EDA) at which the electronic diagram, or electronic schematic of the designed electronic circuit is created by a designer. This is done interactively with the help of a schematic capture tool also known as schematic editor.

The circuit design is the very first step of actual design of an electronic circuit. Typically sketches are drawn on paper, and then entered into a computer using a schematic editor. Therefore schematic entry is said to be a front-end operation of several others in the design flow.

- Schematics.com is a free online schematic editor that allows you to create and share circuit diagrams.

- Scheme-it is a free online schematic drawing tool that will allow you to produce professional looking schematic diagrams, add corresponding part numbers, and share your schematic with others. We have new features. Read about them in our What's New page under Help.

- EasyEDA is a free EDA tool suite free,which is Web, cloud-based and zero-install integrating powerful schematic capture, mixed-mode circuit simulation and PCB layout in a seamless cross-platform browser environment. More Free PCB Softwares.

Schematic Capture Tool is a free online schematic editor that allows you to create and share circuit diagrams. The DipTrace schematic capture module is an advanced circuit design tool that supports multi-sheet and multi-level hierarchical schematics. Circuits can be easily converted to PCB and back annotated. Verification and Spice export for simulation allow for full project analysis. DipTrace’s Schematic capture.

Despite the complexity of modern components – huge ball grid arrays and tiny passive components – schematic capture is easier today than it has been for many years. CAD software is easier to use and is available in full-featured expensive packages, very capable mid-range packages that sometimes have free versions and completely free versions that are either open source or directly linked to a printed circuit board fabrication company.

In past years, schematic diagrams with mostly discrete components were fairly readable. However, with the newer high pin-count parts and with the almost universal use of standard letter or A4 sized paper, schematics have become less so. Many times, there will be a single large part on a page with nothing but pin reference keys to connect it to other pages.

Baseball Games: Strike out each batter, try to hit a grand slam, and win the World Series in one of our many free, online baseball games! Pick One of Our Free Baseball Games, and Have Fun. Put on your baseball cap and get ready for some great baseball games! We got a great collection of the best baseball games and baseball apps. Step up to the plate and see how many home runs you can smack out of the park. Play the best free online baseball games right here! About our Free Baseball Games. Known as 'America's pastime' (though it was originally developed in England and is also widely played in Japan and Cuba and other countries, too), baseball games are one of North America's most beloved sports. It's remained popular for centuries, with leagues ranging from the youngest kids to international associations of professionals. Free baseball games offline.

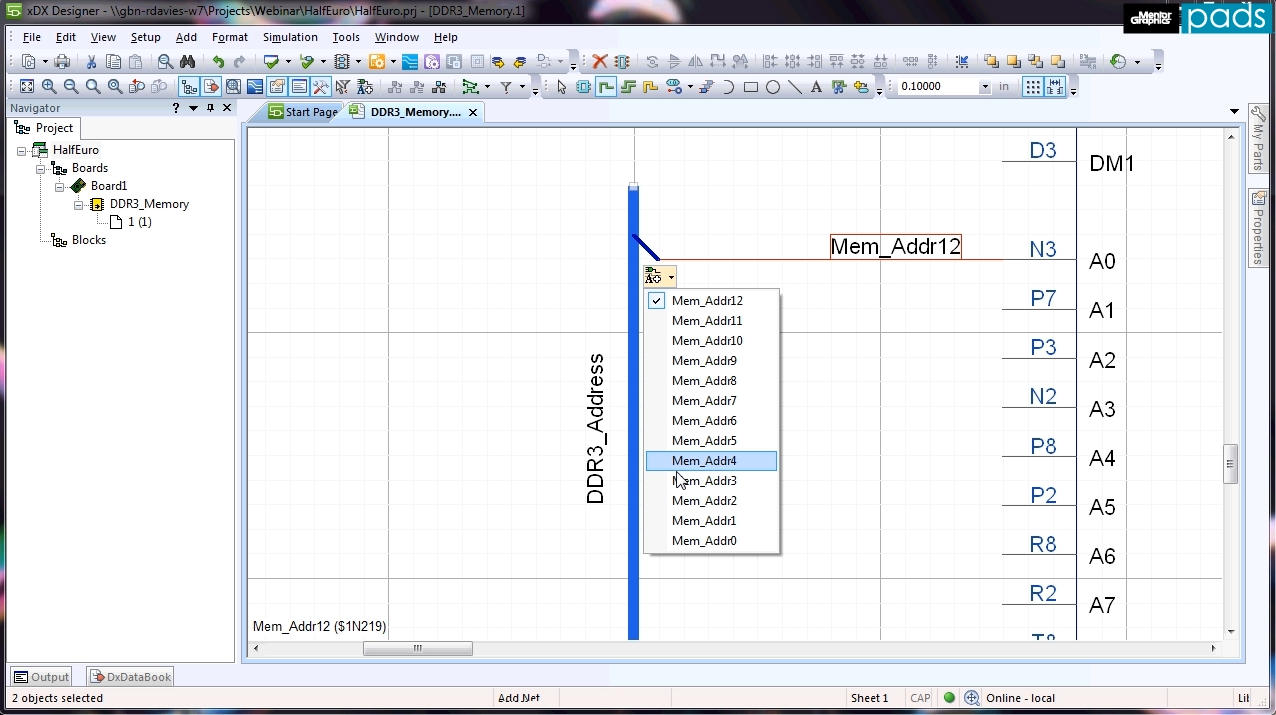

Readability levels can be enhanced by using buses and superbuses, related pins can be connected into a common bus and routed to other pages. Buses don't need to be just the traditional address or data bus directly linked pins. A bus grouping can also be used for related uses, such as all analog input or all communications related pin functions.

Other considerations[edit]

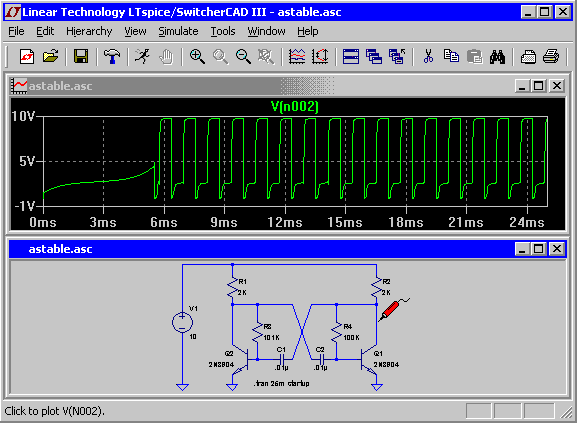

After the circuit design is captured in a schematic, most EDA tools allow the design to be simulated.

Schematic capture involves not only entering the circuits into the CAD system, but also generally calls for decisions that may seem more appropriate for later in the design, such as package choice. Although you may be able to change the package later, many PCB CAD systems ask you to choose both the part and package when placing it into the schematic capture program.

This also brings into play such considerations as prototyping and assembly. In a high-volume assembly environment, there will be plenty of opportunities for DFM analysis. However, in a rapid prototyping environment such as at assembly houses specializing in low-volume/high-mix and quick turnaround times, the pick and place machines are programmed directly from the board layout files. Careful package selection during schematic capture will save time during the assembly and debug process.

Netgear n150 wireless adapter driver. I get just around 40mbps.

With new parts, the CAD system may not have your chosen component in its parts library, so you may need to create the parts library yourself. Again, you may at the time not be overly concerned with the package, but careful creation of the part library will save time and risk later.

After the circuit design is captured in a schematic, then the PCB layout can begin.

Where is the Georgia DMV? The State of Georgia does not have a Department of Motor Vehicles (DMV). In our state, the functions normally associated with a DMV are separated between two agencies: Department of Driver Services (DDS) DDS helps you obtain, renew, or replace learner’s permits, ID cards, and licenses. Department of Revenue (DOR). Renewing your Driver's License by Mail. The Georgia Department of Driver Services offers renewal by mail options under limited circumstances for U.S. Citizen customers who are unable to renew their license in person. The following customers may utilize this option. Georgia drivers license renewal. Applying for a new Georgia Driver's License or Passenger Permit The State of Georgia requires you renew your driver’s license upon expiration. Click here to simplify and find all the details for your renewal in the step-by-step process. Renewing your Georgia Driver's License In Georgia, anyone who has never been issued a driver's license must. You must be a Georgia resident. You must be a US Citizen. Your current license. Customers who set up an account prior to 12/2010 or were required to enter a RIN to renew their Driver's License or Identification Card must also set up a new Customer Account to use our enhanced process. Official Web Site for the Georgia Department of Driver Services. Get all the information you need to get and renew a GA Driver's License, ID or Permit.

See also[edit]

| Wikibooks has a book on the topic of: Robotics: Design Basics: Design software |

| The Wikibook Practical Electronics has a page on the topic of: PCB Layout |

Further reading[edit]

- Pratt, Gary; Jarrett, Jay (2001-08-06). 'Top-Down Design Methods Bring Back The Useful Schematic Diagram'. Electronic Design. 49 (16): 69. ISSN0013-4872. ED Online ID #3784.

Comparison of electronic design automation (EDA) software

Comparison of EDA packages[edit]

| Application and developer | Latest version/release + date | Schematic? | Simulation? | PCB editing? | Runs on POSIX style systems? | Runs on Windows? | Other platforms? | Open source? | User Interface Language(s) | Imports | Exports | Scripting support |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Advanced Design System by Keysight EEsof EDA | 2019 15 November 2018 (10 months ago)[1] | Yes | Yes | Yes | Yes[2] | Yes[2] | SuSE, RHEL[2] | No | en | HSPICE, SPICE, Spectre netlists; Gerber, Excellon, ODB++, artwork; more | HSPICE, SPICE, Spectre netlists; Gerber, Excellon, ODB++, artwork; more | Python, Application Extension Language (proprietary; 'AEL') |

| Active-HDL by Aldec | 10.3 16 March 2016 (3 years ago) | Yes | Yes | No | No | Yes | No | No | en | EDIF, Viewlogic, more | PDF, HTML, Verilog, VHDL, EDIF, Zuken, more | |

| Altium Designer (former Protel) by Altium | 19.0.15 18 April 2019 (5 months ago) | Yes | Yes | Yes | No | Yes | Wine | No | Multilingual | OrCAD, Allegro, PADS Logic, PADS PCB, Expedition, DxDesigner, EAGLE, Gerber, STEP, Solidworks, IDF, more | 3D PDF, Gerber, Gerber X2, Excellon, ODB++, DXF, STEP, OrCAD, EAGLE, more | Delphi, JS, VB |

| CADSTAR, Board Designer, and Visula by Zuken | 18 30 June 2017 (2 years ago) | Yes | Yes, Spice | Yes | No | Yes | No | No | en | PADS, OrCAD, P-CAD, Protel, DXF, IDF | PDF, Gerber, Excellon, ODB++, DXF, IDF more | |

| CircuitLogix by Logic Design Inc. | Release 9.1 January 2013 (6 years ago) | Yes | Yes | Yes | No | Yes | No | No | en | SPICE, Gerber, DXF | SPICE, PDF, Gerber, DXF | |

| CircuitMaker by Altium | 1.3.0.119 August 2016 (3 years ago) | Yes | No | Yes | No | Yes | Wine | No | en | AD09, AD10, AD12, PADS, P-CAD, OrCAD, Protel, EAGLE, DXF | Gerber, Excellon, DXF, STEP, more | |

| CircuitStudio by Altium | 1.5.1.13 25 May 2018 (16 months ago) | Yes | Yes | Yes | No | Yes | Wine | No | en | AD09, AD10, AD12, PADS, P-CAD, OrCAD, Protel, EAGLE, DXF | Gerber, Excellon, SPICE, DXF, STEP, more | |

| CR-5000 by Zuken | 13 17 May 2011 (8 years ago) | Yes | Yes, SI & PI | Yes | Yes | Yes | Unix, Linux | No | en, jp | EDIF, DXF, IGES, IDF, BSDL, STEP, ACIS, Gerber, Excellon, more | PDF, Gerber, Excellon, ODB++ (must request[3]), DXF, STEP, IPC D-356, IPC-2581, EPS, ACIS | |

| DipTrace by Novarm | 3.3.1.0 29 November 2018 (10 months ago) | Yes | External (Spice netlist export) | Yes | Yes | Yes | Mac, Wine | No | 21 languages | EAGLE, Altium, P-CAD, PADS, OrCAD, Gerber, N/C Drill, DXF, BSDL Pinlist, Netlists | Gerber, Gerber X2, Excellon, ODB++, DXF, P-CAD, PADS, OrCAD, IPC-D-356, STEP, VRML, Pick and Place, CSV, BOM | |

| DesignSpark PCB from RS Components | 8 16 June 2016 (3 years ago) | Yes | Yes, Spice | Yes | No | Yes | No | No | Various | EAGLE, DXF, EDIF | Gerber, Excellon, ODB++, DXF, IDF, PDF, LPKF | |

| EAGLE by Autodesk/CadSoft Computer | 9.3.2 21 March 2019 (6 months ago) | Yes | Ngspice | Yes | Yes | Yes | Linux, Mac | No | de, en, zh, hu, ru | EAGLE (XML), ACCEL (P-CAD, Altium, Protel), ULTIBOARD, Netlists, BMP, Custom | EAGLE (XML), Protel, Netlists, Images, Gerber, Gerber X2, Excellon, Sieb & Meyer, HPGL, PostScript/EPS, PDF, Images, HyperLynx, IDF, Custom | Proprietary User Language Programming (ULP) |

| EasyEDA | 5.4.12 7 May 2018 (16 months ago) | Yes | Ngspice | Yes | Yes | Yes | Linux, Mac, and Chrome OS as a Web application | No | en, fr, de, pl, jp, ru, es, se, ua, zh .. | Altium, EAGLE, KiCad libraries, LTspice .asc/.asy files, JSON, Spice | PDF, PNG, SVG, JSON, Gerber, Excellon, Pick and Place CSV file, CSV-formatted drill chart, Bill of Materials CSV file, Altium netlist, FreePCB netlist, PADS Layout Netlist, Spice netlist. | JSON |

| Fritzing | 0.9.3b[4] 3 June 2016 (3 years ago) | Yes, + breadboard | No | Yes | Yes | Yes | Linux, Mac | Yes | en, de, nl, es, it, fr, pt, ru, zh, jp, .. | gEDA symbols, KiCad symbols, SVG | Gerber, DIY etching, BOM, SVG, PDF, EPS | |

| gEDA | 1.8.2[5] 25 September 2013 (6 years ago) | Yes | Yes | Yes | Yes | Yes | Linux, Mac | Yes | en | gschem netlists, image as background | Gerber, Excellon, SVG, PDF, EPS, PNG, GIF, JPEG, Specctra, XYRS | yes |

| KiCad | 5.1.4[6] 14 August 2019 | Yes | Internal: Ngspice External: SPICE netlist export | Yes | Yes | Yes | Linux, Mac | Yes | zh_CN, de, en, es, fr, it, pt, ru, ja, pl, cz | TinyCAD net lists, OrCAD EDIF, EAGLE (XML) | PDF, Gerber, Gerber X2, Excellon, netlist, VRML2, STEP, IDFv3 | Python |

| OrCAD | 17.2 October 2016 (3 years ago) | Yes | Yes | Yes | No | Yes | No | No | en | EAGLE, PADS, Altium, STEP, DXF, IDF, IDX, OrCAD SDT, OrCAD Layout,OrCAD | PDF, Gerber, Gerber X2, Excellon drill/route, netlist, ODB++, DXF, IDF, IDX, STEP,3D PDF, IPC2581 | Tcl/TK, SKILL (Lisp) |

| pcb-rnd | 2.0.0[7] 6 June 2018 (16 months ago) | No | No | Yes | Yes | No | Linux, Mac | Yes | en | gschem netlists, Protel Autotrax, KiCad (legacy & s-expr layouts), EAGLE (XML & v3,4,5 binary layouts), eeschema netlists, mentor netlists, TinyCad netlists, LT-Spice, MUCS, Specctra, Mentor Graphics Hyperlynx, BMP, JPG, GIF, HPGL, image as background | Gerber/[Excellon format|drill],SVG, PDF, EPS, PNG, GIF, JPEG, Specctra, Protel Autotrax, KiCad (legacy & s-expr), DXF, FidocadJ, Mentor Graphics Hyperlynx, template configurable XYRS/BOM | Multiple languages |

| Upverter | 10 May 2019 (4 months ago) | Yes | No | Yes | Yes | Yes | Web application | No | en | Altium, OrCad, PDF, OpenJSON, EAGLE | PDF, Gerber, Excellon, netlist, PADS Layout Netlist, Tempo Automation, Pick and Place CSV, High-Res PNG, STL, CSV-formatted drill chart, CSV-formatted list of all parts | |

| Micro-Cap by Spectrum Software | 11.0.2.0 3 September 2016 (3 years ago) | Yes | Yes | No | No | Yes | Wine | No | en, jp | HSPICE, PSPICE, SPICE3, netlists, Images, IBIS, Touchstone | SPICE text file, netlist, BOM, Protel, Accel, OrCad, PADS netlists, Schematic and Analysis Plots Images, Numeric Output Text, Excel | |

| Pulsonix by WestDev Ltd | 10.0 1 October 2018 (12 months ago) | Yes | Yes | Yes | No | Yes | Wine | No | en | Allegro, Altium, CadStar, EAGLE, OrCAD, PADS, P-CAD, Protel, Gerber, STEP, DXF, IDF, more | Gerber, Gerber X2, Excellon, ODB++, IPC-2581, PDF, DXF, STEP, IDF, BOM, more | Proprietary language, ActiveX |

| TARGET 3001! | 20.3.0.64 29 April 2019 (5 months ago) | Yes | Yes | Yes | No | Yes | No | No | en, de, fr | EAGLE, DXF, Gerber, XGerber, Excellon, BMP, CXF, STEP 3D | XGerber, Excellon, EAGLE, HPGL, G-Code (Milling), CXF, STEP 3D, Excel BOMs, Pick&Place, GenCAD, FABmaster, IPC D-356, Test points, Netlists, OBJ, POV-Ray, PDF | |

| NI Ultiboard and Multisim by National Instruments | 14.1 1 March 2017 (2 years ago)[8] | Yes | Yes | Yes | No | Yes | Web application[9] | No | en | MS*, MP*, EWB, Spice, OrCAD, UltiCap, Protel, Gerber, DXF, Ultiboard 4&5, Calay | BOM, Gerber, Excellon, IGES (3D), DXF (2D & 3D), SVG | |

| 123D Circuits by Autodesk | N/A | Yes, + breadboard | Yes | Yes | Yes | Yes | Web application | No | en | EAGLE | Gerber | |

| Application and developer | Latest version/release + date | Schematic? | Simulation? | PCB editing? | Runs on POSIX style systems? | Runs on Windows? | Other platforms? | Open source? | User Interface Language(s) | Imports | Exports | Scripting support |

Note: ODB++ support is drawn partly from lists by Artwork Conversion Software[3] and Mentor Graphics[10] Mummy games to play 2017.

Free software[edit]

| Name | Architecture | License | Autorouter | Comment |

|---|---|---|---|---|

| Electric | *BSD, Java | GPL | Yes | VLSI circuit design tool with connectivity at all levels. Can also be used for schematic entry and PCB design. |

| FreePCB | w32 | GPL | Yes | A printed circuit board design program for Microsoft Windows. FreePCB allows for up to 16 copper layers, both metric and US customary units, and export of designs in Gerber format. Boards can be partially or fully autorouted with the FreeRouting[11] autorouter by using the FpcROUTE Specctra DSN design file translator. |

| Fritzing | Windows, Mac, Linux | GPL | Yes | Protoboard view, schematic view, PCB view, Code (firmware) view. Includes customizable design rule checker. Includes common shaped boards like Arduino and Raspberry Pi shields. Allows spline curve traces. Only two layers (top and bottom). Outputs gerbers. |

| gEDA | *BSD, Linux, Mac | GPL | Yes | schematic, simulation, PCB editor, gerber view |

| Gnucap | any (C++98) | GPL3 | Mixed-signal circuit simulator | |

| Icarus Verilog | *BSD, Linux, Mac | GPL | Verilog simulator | |

| KiCad | Linux, Mac, Windows | GNU GPL | Built-in, or FreeRouting | Full package for schematic and board design, etc. Design rule checking. User-defined symbols and footprints. Gerber/ drill file creation. Graphic interface. Active user community. |

| KTechLab | Linux | GPL | n/a | KTechLab is a schematic capture and simulator. It is specifically geared toward mixed signal simulation of analog components and small digital processors. |

| Magic | Linux | BSD license | no | A popular very-large-scale integration layout tool |

| Ngspice | Linux, Solaris, Mac, NetBSD, FreeBSD, w32 | BSD | SPICE + XSPICE + Cider | |

| Oregano | GPL | no | Schematic capture + spice simulation | |

| Quite Universal Circuit Simulator (QUCS) | Linux, Solaris, Mac, NetBSD, FreeBSD, w32 | GPL | Schematic capture + Verilog + VHDL + simulation | |

| pcb-rnd | *BSD, Linux, Mac | GPL | yes | Circuit layout program with extended file format support, DRC, parametric footprints, query language, and GUI and command line operation for batch processing and automation |

| Verilator | Posix | GPL | Verilator is the fastest free Verilog HDL simulator. It compiles synthesizable Verilog into cycle accurate C++ or SystemC code following 2-state synthesis (zero delay) semantics. Benchmarks reported on its website suggest it is several times faster than commercial event driven simulators such as ModelSim, NC-Verilog and VCS, while not quite as fast as commercial cycle accurate modeling tools such as Carbon ModelStudio and ARC VTOC. | |

| XCircuit | Unix | GPL | Used to produce netlists and publish high-quality drawings. |

See also[edit]

- SPICE, a general purpose analog circuitsimulator.

Free Schematic Capture Tool

References[edit]

- ^Advanced Design System – ADS Software - Current Version

- ^ abc'ADS Supported Platforms'. Archived from the original on 2017-10-15. Retrieved 2015-03-20.

- ^ ab'PCB tools supporting ODB++'. Artwork.com. Artwork Conversion Software Inc. Retrieved 2011-09-25.

- ^http://blog.fritzing.org/2016/06/03/new-fritzing-release-0-9-3b/

- ^http://wiki.geda-project.org/geda:download

- ^'KiCad 5.1.4 Release'. KiCad 5.1.4 Release.

- ^http://repo.hu/projects/pcb-rnd/news.html

- ^'Latest Multisim Release'.

- ^'Multisim Web App'. Archived from the original on 2017-04-19. Retrieved 2017-04-18.

- ^'ODB++ Data Exchange'. Mentor.com. Mentor Graphics. Archived from the original on 2012-10-06. Retrieved 25 September 2011.

- ^Wirtz, Alfons (2014-03-08) [2004]. 'FreeRouting - Printed Circuit Board Routing Software from FreeRouting.net'. Archived from the original on 2017-09-24. Retrieved 2017-09-24.